基于verilog的正弦波发生器

这是我在CSDN里的第一篇文章,先做个小广告。。

我建了一个嵌入式和FPGA的公众号,里面也是我写的一些文章,有的是平时学习的笔记,或者实验的记录,我希望和大家一起学习,记录学习的东西。因为刚刚起步,需要大家的支持,希望大家关注一下,也可以给我点建议。。

毕竟是刚刚起步,文章写的不好,大家别介意,一起努力哈哈哈

*

公众号:FPGA科技室

**

已改名为:FPGA科技室

这一篇文章是关于基于verilog的正弦波发生器(即产生正弦波波形),这也是我的公众号第一篇FPGA文章,想让大家学习一下如何利用开发工具,产生一个正弦波形sinx。

为啥开篇讲这个内容呢,因为毕竟第一篇文章,适合循序渐进,从简单先入手,但大家不要小看这个正弦波波形的设计,因为这将会是直接数字式频率合成器DDS的基础,只有会第一步设计,我们才能更加深入到DDS,之后我也会来讲述。

开门见山,这次的设计要用到matlab软件(生成ram ip核的mif文件),multisim 10(仿真波形),UE(编写代码)。 想必大家学过数字信号处理DSP,如果要采样信号,则其采样频率必须大于原信号最高频率的两倍,即fs>=2fc。ram既然是数字器件,我们无法存入模拟信号正弦波,则需要对其进行采样定点化(一般fpga器件无法存浮点数,需要定点化),那么我们就用到了matlab,利用其强大的功能,编写matlab程序,得到采样点值,并利用matlab生成mif文件(ram的初始化文件)

下面就是大致的设计思路:

将连续的正弦波信号进行离散化;应用matlab 软件进行实现;

2.将离散化后的正弦波一个整周期存储到Ram中;

(1).将离散后的数据进行定点化,Ram的规格是256x8,数据规格1bit符号位和7比特小数位。

(2).创建一个Ram 用于存储离散数据

首先我先给出matlab代码:

**

N=2^8; %N为采样点数

s_p=0:255;%正弦波一个周期的采样点数

sin_data=sin(2*pi*s_p/N); %sin_data是初步采样值,浮点数% 编写到这里,大家可以在任务行中显示此时的波形

fix_p_sin_data=fix(sin_data*127); %定点化 fix()函数可以直接去除小数点后的值,使之成为整数

for i=1:N

if fix_p_sin_data(i)<0

fix_p_sin_data(i)=N+fix_p_sin_data(i)

else

fix_p_sin_data(i)=fix_p_sin_data(i);

end

end%下面是mif文件固定格式,不可更改

fid=fopen('sp_ram_256x8.mif','w+');

fprintf(fid,'WIDTH=8;\n');

fprintf(fid,'DEPTH=256;\n');

fprintf(fid,'ADDRESS_RADIX=UNS;\n');

fprintf(fid,'DATA_RADIX=UNS;\n');

fprintf(fid,'CONTENT BEGIN \n');

for i=1:N

fprintf(fid,'%d:%d; \n',i-1,fix_p_sin_data(i));

end

fprintf(fid,'END; \n');

fclose(fid);

好了到此为止,我们就编写完并生成了初始化**mif文件了,下面可以开始verilog编写了,噢,不对,咱们先来利用quartus

生成一个ip ram,因为verilog编写时需要例化IP哦

我们来生成RAM。。。。首先利用ip工具,create a new ip

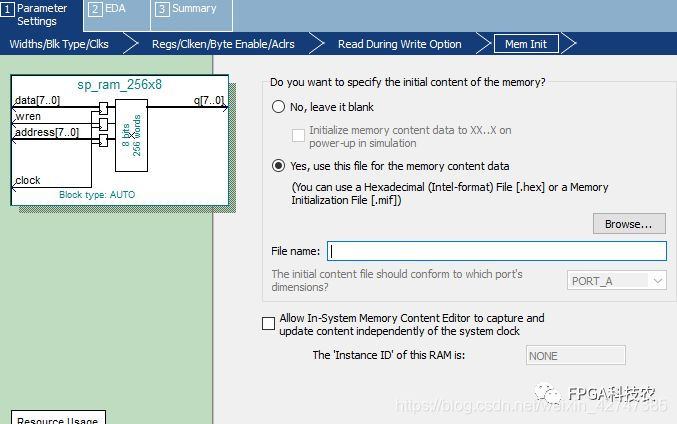

选择类型。。。。。咱们这次用单口ram ,sp_ram_256x8

如下图是我们创建的ram,256深度,位宽为8哦

最后我们加入刚刚matlab生成的mif文件

完成了一半了,此时我们可以在工作区看到我们新建的ip核工程了

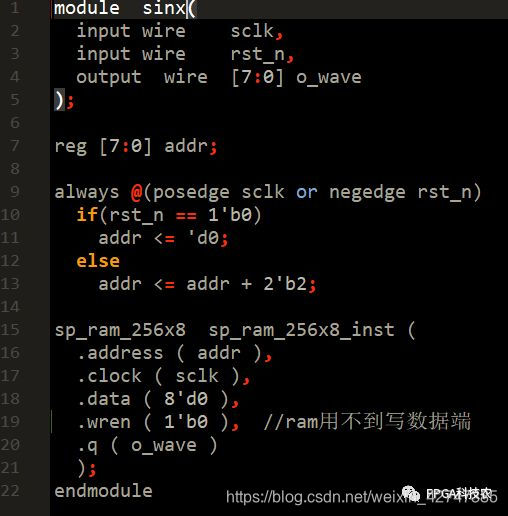

下面来编写verilig代码,顶层文件:在顶层中例化了ip核 ,由于我们已经初始化了mif,则ram的写数据端用不到,我们将其置为0,数据也为0,只由地址端进行操作。

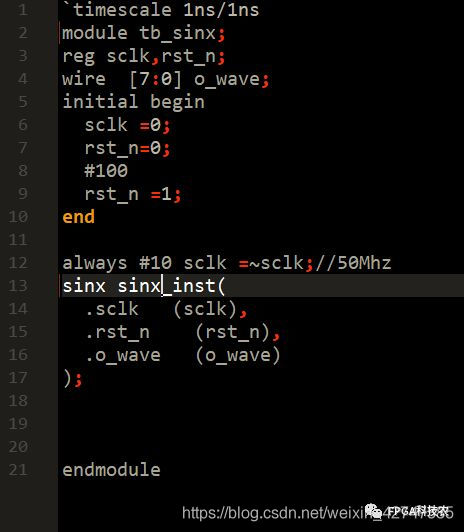

至此,只要再编写testbench文件即可,

ok,至此我们完成了正弦波的设计,

来吧,这下我们来个仿真,见证奇迹的时刻

总结:

咦,不知道大家发现没,如果按照这样的mif编写规则,我们是不是不光可以生成sinx波形,还可以生成cosx。。。等等的函数波形,因为matlab很强大,帮助了我们很多,这次的设计虽然简单,但是用到了挺多东西,如何建立ip核,如何初始化。。可见设计一样东西,需要全面的知识体系,verilog只是一个工具。

哈哈,第一篇文章结束了,写的不难懂吧,用通俗的话,主要描述了操作。大家可以试试哦

发挥部分:如何实现正弦波的频率可调?

转载自原文链接, 如需删除请联系管理员。

原文链接:基于verilog的正弦波发生器,转载请注明来源!